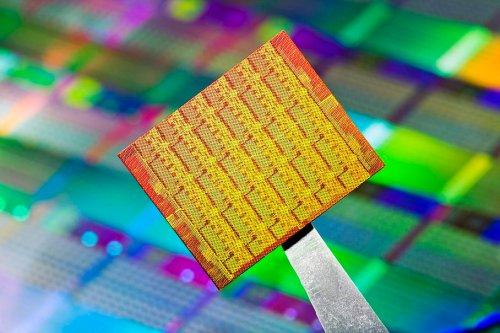

Intel présente un CPU 48 cœurs !

jeu, 03/12/2009 - 14:25

Alors qu'Intel va intégrer des fonctions essentielles dans une nouvelle ligne de processeurs Intel Core en début d’année prochaine, avec la sortie de processeurs à six et huit cœurs prévue courant 2010, ce prototype comporte quarante-huit cœurs (ou plus exactement 24 double cœurs) de traitement totalement programmables. Il dispose aussi d’un réseau intégré à haute vitesse pour le partage des informations ainsi que des techniques originales de gestion électrique qui permettent à l’ensemble de ses cœurs de travailler à un très haut rendement énergétique, soit à une puissance d’à peine 25 watts au ralenti et 125 watts en performances maximales (environ autant que les processeurs actuels ou l’équivalent de la puissance consommée par deux ampoules ménagères).

Intel prévoit de mieux comprendre comment ordonnancer et coordonner les cœurs de cette puce expérimentale, pour ainsi en faire profiter ses futurs processeurs courants. Ainsi, de futurs PC portables dotés de capacités de traitement de cette magnitude pourraient bénéficier d’une « vision », au même titre qu’un être humain voit les objets et les mouvements en temps réel avec une grande précision.

On peut donc imaginer, un jour, d’interagir avec un ordinateur pour une leçon de danse virtuelle ou pour faire des achats en ligne avec une future caméra 3D intégrée à l’ordinateur, qui affichera une image de soi-même portant les vêtements repérés sur le catalogue en ligne. Il suffira de bouger pour juger du drapé d’un tissu ou de la manière dont la couleur du vêtement s’accorde au teint de celui qui le porte.

Ce type d’interactions pourrait dispenser des claviers, des télécommandes et des manettes pour les jeux. Certains chercheurs estiment d’ailleurs que les ordinateurs pourront même un jour déchiffrer les ondes cérébrales et qu’il suffira de penser une commande, par exemple un texte à dicter, pour que l’opération s’effectue sans avoir à prononcer un mot.

Les Intel Labs ont surnommé cette puce « single-chip cloud computer » (ordinateur monopuce « virtuel » ou « nébuleux ») parce qu’elle ressemble à l’agencement des datacenters utilisés pour créer un « nuage virtuel » de ressources informatiques accessibles via Internet, afin de proposer des services tels que la banque en ligne, les réseaux sociaux et les sites marchands à des millions d’utilisateurs.

Ces centres de données « virtuels » ou « nébuleux » se composent en effet de dizaines de milliers d’ordinateurs reliés par un réseau de câbles et répartissent des tâches lourdes ou des fichiers massifs en parallèle. Or c’est justement une approche similaire qu’emploie la nouvelle puce expérimentale d’Intel, même si tous les ordinateurs et les réseaux y sont intégrés sur une même matrice de silicium, 45 nm « high-k » de la taille approximative d’un timbre, ce qui réduit considérablement le nombre d’ordinateurs physiques nécessaire à la mise en place d’un centre de données « nébuleux ».

Justin Rattner, responsable des Intel Labs et Chief Technology Officer d’Intel : « Avec une puce comme celle-là, on peut imaginer un datacenter nébuleux qui sera plus économe en énergie d’un ordre entier de grandeur que ceux qui existent aujourd’hui, soit d’importantes économies de ressources en place et en électricité. A terme, j’estime que ces concepts de pointe s’appliqueront aux appareils courants, de même que des technologies automobiles de pointe comme la commande électronique du moteur, les airbags et les systèmes de freinage ABS ont fini par se retrouver sur toutes les voitures. »

Des cœurs qui permettent aux logiciels de diriger intelligemment les données

Cette « concept chip » dispose d’un réseau haute vitesse qui relie ses cœurs pour le bon partage des informations et des données. Cette technique apporte une importante amélioration aux performances de communication et au rendement électrique par rapport au modèle actuel des centres de données, car les paquets de données n’ont à se déplacer que de quelques millimètres sur la puce au lieu de plusieurs dizaines de mètres vers un autre ordinateur.

Les logiciels d’application peuvent ainsi exploiter ce réseau pour transmettre directement l’information entre les cœurs coopérants, en quelques microsecondes à peine, ce qui dispense de l’accès aux données dans une mémoire externe à la puce. Les applications peuvent aussi très précisément gérer en dynamique ceux des cœurs à utiliser pour une tâche donnée à un instant donné, en faisant correspondre les besoins en performances et en énergie aux contraintes de chacun.

Les tâches annexes peuvent se réaliser sur des cœurs proches, en transmettant même les résultats d’un cœur au suivant, comme sur une chaîne de production, pour maximiser les performances globales. Ce contrôle logiciel se complète par ailleurs de la capacité à gérer la tension et la fréquence d’horloge : les cœurs peuvent s’éteindre et s’allumer ou encore régler leur niveau de performances, en s’adaptant ainsi en continu pour utiliser le minimum d’énergie à chaque instant.

Réponse aux enjeux logiciels

La programmation de processeurs multicœurs représente une difficulté bien connue du secteur informatique, à l’heure ou les constructeurs d’ordinateurs et les éditeurs de logiciels s’orientent vers un grand nombre de cœurs sur une même puce. Le prototype se prête à des approches de programmation parallèle courantes et efficaces, utilisées par les logiciels de datacenters virtuels. Des chercheurs d’Intel, HP et de la collaboration Open Cirrus de Yahoo ont déjà entamé le portage d’applications nébuleuses sur cette puce à l’aide d’Hadoop, cadre logiciel Java qui gère les applications réparties et fortement manipulatrices de données telles que pour la démonstration de Justin Rattner.

Intel prévoit de fabriquer une centaine de ces puces expérimentales, à distribuer pour leur usage par plusieurs dizaines de collaborateurs de recherche du secteur et du monde universitaire dans le monde, l’objectif étant l’élaboration d’applications logicielles et modèles de programmation pour les futurs processeurs très multicœurs. L’une des institutions européennes qui utilisera la puce d’Intel pour de futures recherches est l’Ecole polytechnique fédérale de Zurich (ETHZ).

Pr Timothy Roscoe, du département d’informatique de l’ETHZ : « Nous sommes très intéressés par le single-chip cloud computer d’Intel. Dans le cadre du projet Barrelfish, nous concevons en effet des architectures de systèmes d’exploitation pour les futurs systèmes pluricœurs et multicœurs. Le système mémoire de cette puce et le support à la transmission de messages sont donc parfaits pour nous et c’est un véhicule idéal pour tester et valider nos idées. »

Cette innovation constitue le dernier résultat marquant du programme Intel de recherche en téra-informatique, qui vise à surmonter les barrières vers de futures puces dotées de plusieurs dizaines, voire centaines, de cœurs. Il a été mis en place concomitamment par les Intel Labs dans leurs centres de recherche de Bangalore (Inde), Braunschweig (Allemagne) et Hillsboro (Oregon). C’est le centre de Braunschweig, qui fait partie des Intel Labs Europe, qui a conçu le cœur du processeur, le matériel spécialisé qui permet aux cœurs de communiquer avec une latence réduite ainsi qu’un contrôleur mémoire rationalisé et économe en énergie, optimisé pour un design très multicœur. Responsable des actions de validation pour l’ensemble de la puce, l’équipe allemande a appliqué une technologie propriétaire d’émulation de microprocesseurs qui a permis à l’équipe mondiale de tester des concepts logiciels et matériels avant la fabrication de la puce proprement dite. Cette démarche a ainsi réduit les délais d’études de moitié environ et accéléré le développement logiciel. Les détails de l’architecture et des circuits de la puce seront publiés dans un article proposé à l’International Solid State Circuits Conference de février.